Serial Flash Reset Signaling Protocol (SFRSP) 是由JEDEC定义的一套适用于串行Flash的标准,即JESD252.01标准。JESD252.01文档篇幅不长,描述了一种信号协议,以允许主机在没有专用硬件复位引脚的情况下复位目标串行Flash设备。

JEDEC会不断发布新版本的JESD252.01规范,最新版本可在JEDEC官网下载(需注册账户)。本博客文档是基于JESD252.01编写的。JESD252.01各版本信息如下:

| 版本 | 地址(官方下载需登录) | 备注 |

|---|---|---|

| JESD252.01 | 官方下载,三方下载 | 发布于2021年,是JESD252.01规范的第一版 |

该标准定义了一种信号协议,允许主机在没有专用硬件复位引脚的情况下复位目标串行Flash设备。一些串行Flash设备提供一个专用的RESET#引脚,可以用来在设备上执行硬件复位。在这种情况下,当主机设置RESET#一段时间后串行Flash设备将被硬件复位。一些串行Flash设备可能不提供这种功能的RESET#硬件引脚,要么受限于封装的大小,要么根据设计与I/O引脚共享。在共享引脚的情况下,如果I/O引脚被用于Quad或Octal配置,则复位功能将被禁用。此外,即使在串行Flash设备上有一个RESET#硬件引脚,也不可能有一个专用的主机IO引脚来控制RESET#信号。本标准指定了一种信号协议,可以令串行Flash接口上实现在没有专用硬件复位引脚的情况下执行硬件复位。如果主机和设备都支持该协议,则用户只需使用cs#、SCK和SI引脚即可实现硬件复位功能。

1 范围

这个标准定义了串行Flash设备硬件复位信号协议。该协议可以在设备没有专用 RESET#引脚的情况下使用。

2 规范性引用文件

下列规范性文件所包含的条款通过在本标准中引用而构成本标准的条款。对于标注日期的参考文献,这些出版物的后续修订或修订均不适用。然而,基于本标准达成协议的各方应研究采用所述规范性文件的最新版本的可能性。凡引用的规范性文件未注明日期的,适用最新版本。

JEDEC Manual, JM7.01:JEDEC标准和其他出版物的样式手册。

JEDEC Standard, JESD88E:固态技术术语词典。

JEDEC Standard, JESD99C:微电子设备的术语、定义和字母符号。

JEDEC Standard, JESD100B.01:微型计算机、微处理器和存储器集成电路的术语、定义和字母符号。

JEDEC Standard, JESD216:串行Flash可发现参数(SFDP)。

JEDEC Standard, JESD251:扩展串行外围接口(xSPI)的非易失存储器设备。

3 术语和定义

JESD88(固态技术术语词典)的当前版本是本标准中所用术语的管理文件。为便于参考,提供了以下术语和定义:

CS#:设备片选引脚。

IO0:串行输入输出0(一些旧的设备将该信号称为SI)。

IO1:串行输入输出1(一些旧的设备将该信号称为SO)。

SCK:设备串行时钟。

4 协议描述

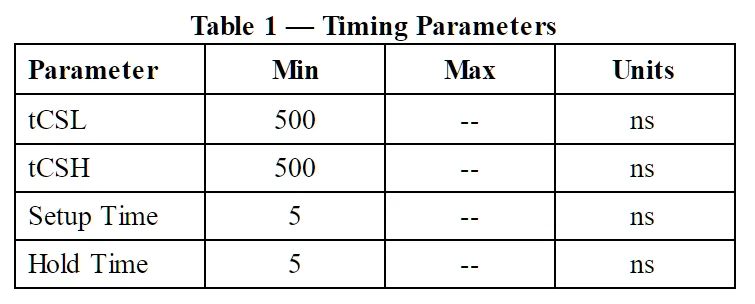

复位信号协议如时序图所示,该协议包括两个阶段:复位请求和完成(设备内部复位)。

4.1 复位请求

- CS# 驱动为低有效来选中SPI目标(注1)。

- 时钟(SCK)在高或低状态下保持稳定(注2)。

- SI/IO0驱动为低电平,同时CS#变为低电平(注3)。

- CS# 驱动为无效(注4)。

每次交替SI状态时重复步骤1-4(注5)。

注1:这将为SPI目标供电。

注2:这可以防止与命令混淆,因为没有传输任何命令位(时钟)。

注3:在SCK转换之前的CS#低期间,没有SPI总线目标驱动SI,即在SCK的第一个边缘之后,才允许目标流输出活动。

注4:目标在CS#上升边缘捕获SI的状态。

注5:SI在第一个CS#是低的,在第二个是高的,在第三个是低的,在第四个是高的(这提供了一个5h模式,以区别于随机噪声)。

4.2 复位完成

在第四个CS#脉冲后,目标触发内部复位。

4.3 时序图和时序参数

{ border-effect="line" thumbnail="true" }

{ border-effect="line" thumbnail="true" }

4.4 协议的补充说明和注意事项

注1:此复位序列不用于正常启动。

注2:此复位序列可在设备可能处于的任何状态下运行。

注3:在复位过程中,设备可能会忽略任何命令。